|

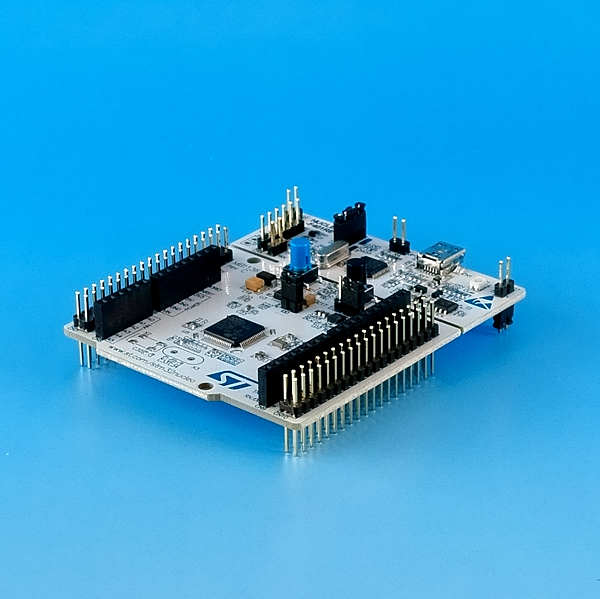

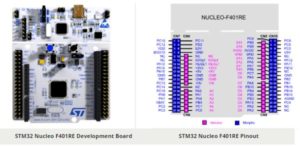

Next up is setting up two other pieces of the M4’s peripherals: I need the DMA controller to pick up all those delicious pixelreadings from the ADC. I was hoping to see exactly during which of the four clock cycles the CCD would feed me the output, but I don’t really feel smarter Īs with women there are still many things I don’t quite understand about CCD’s. Here’s a plot of the CCD master clock (running at 1.4 MHz) with the output signal at every 4th clock cycle: The datasheet finally makes more sense to me (though I still find it confusing that ICG period is called the readout time, when clearly all reading is done 10.6 ms after each ICG pulse). The SH is not shown but here it runs with a period of only 400 µs.Īpparently the SH and ICG need only fulfill the requirements when both trigger, and SH does indeed control the integration time. It’s my first 1D-selfie! The red line is the ICG-pulse running with a period of 40 ms and the blue is the output from the CCD. On two other GPIOs not shown here are the master clock, running at 1.4 MHz, and the ADC clock at 350 kHz. The blue line is the SH pulse and the red is the ICG pulse. However, having the Cortex-M4 timers, it proved quite manageable, and after waking up one night remembering an ARM timing register called something-Polarity and only a few trial runs, I finally had this: However, these application notes from Toshiba explain the different pulses a little better, and the datasheets for similar chips – namely the TCD1254 and TCD1103 – are also instructive.Įven though I felt smarter after reading I still had a nagging suspicion it would be a small nightmare to fulfill the timing criteria of the chip. This, together with the timing diagram in the previous post, is about as much information the datasheet provides. Here are the timing requirements for the TCD1304: And as with women timing is everything with CCD’s. For an up-to-date version and a more well structured presentation go to tcd1304.wordpressĬCD’s are just like women, demanding but wonderful creatures. PA5, PA6, and PA7 are connected to LD_1, LD_2, and LD_3 as shown in the next table.This post from 2015 introduced the very first firmware for driving the tcd1304dg. This board contains the STM32F401RE, a 32-bit microcontroller with an ARM Cortex-M4 core. The Nucleo-F401RE board is used for all the examples.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed